X1のPCG定義部分というのは、あまり詳しい説明を見た記憶がなく謎に包まれている。

資料によっては、1ライン分のデータを出力してから111us待つ文献もある。

(2ライン分待っているのかもしれない)

一方で、24倍速、48倍速といったPCG定義ルーチンでは、

1ラインあたり62.5us程度のゲートタイムなのだ。

また、PCGを定義する場合、一般的にX1のWIDTH 80モードでは、

定義しようとしているPCG番号を特定のTEXT RAM領域に48バイト書き込むことになっているが、

なんと!プログラムによっては、44バイトしか書き込んでいない。

62.5usという時間は、15kHzモニタの1ライン分 + HBLANK(水平帰線期間)である。

X1のWIDTH 80モードでは、1ラインあたり、HBLANKも含めて112文字分を想定しており、

44文字分のアクセス所要時間を計算すると62.5 ÷ 112 × 44 = 24.55us 程度

少なくともラインの始まりから24.55us以内に1ライン分のPCGが定義されるものと推測される。

仮にデータの出力に24.55us秒かかり、さらに62.5usのウェイトを入れたとしたら、

次ライン以降でアクセス位置がずれ、44文字以降の地点になってしまう。

これも考慮に入れると、データの出力にかけられるのは、

24.55 ÷ 8 = 3.069us 程度

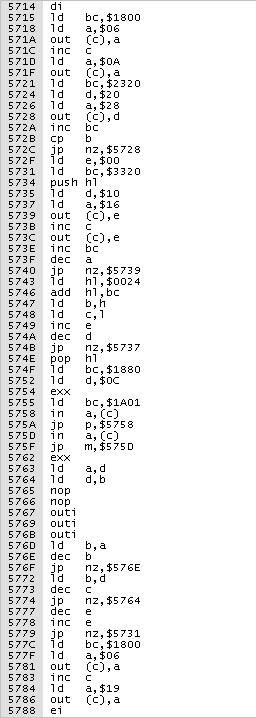

実際のプログラムを見るとOUTI x 3色分で12usかかっている。

どうなっているのか?

このあたりは絶妙で(いや、当たり前か?)、データの出力部分も合わせて

62.5us秒程度で回るように調整されている。

これでデータの出力自体に20us程度までかかっても問題が無い計算になる。

また、当時のDRAMのアクセスタイムについては、

どんなに遅く見積もっても150ns程度(実際のところ、この速度は遅いROMと同程度)なので、

RAMのアクセス速度という観点からするとまったく驚くには値しない。

|